全球领先的科技公司西门子正式发布了其下一代全面硬件辅助验证系统。这一创新平台的问世,标志着集成电路(IC)设计验证领域迈入了一个全新的阶段,旨在应对日益复杂的设计与日益紧迫的上市时间压力所带来的双重挑战。

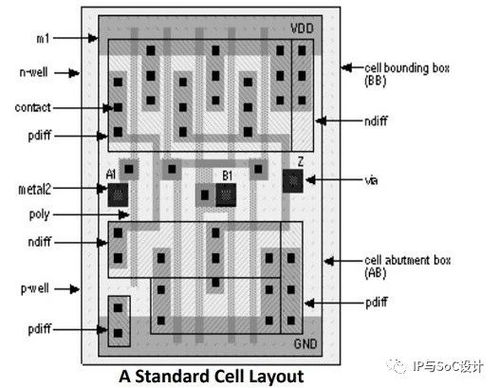

随着人工智能、高性能计算、5G/6G通信和自动驾驶等技术的飞速发展,现代芯片的规模与复杂度呈指数级增长。传统的软件仿真验证方法虽然不可或缺,但在处理超大规模设计时,往往面临速度瓶颈,难以在项目周期内完成充分的验证覆盖。硬件辅助验证,特别是基于现场可编程门阵列(FPGA)的原型验证和仿真加速技术,已成为确保芯片功能正确性、提升验证效率的关键环节。

西门子此次发布的下一代系统,并非单一工具,而是一个高度集成、全面协同的硬件辅助验证平台。其核心优势主要体现在以下几个方面:

1. 无与伦比的性能与容量: 新系统采用了最先进的FPGA架构与互联技术,提供了前所未有的处理能力和系统容量。它能够支持早期软件开发、硬件/软件协同验证以及全系统性能建模,使得设计团队能够在流片前数月就在实际硬件上运行完整的软件栈,极大加速了系统集成与调试进程。

2. 智能化的编译与调试流程: 面对将数亿门级的设计映射到硬件平台的复杂性,新系统集成了智能编译算法,显著缩短了设计编译时间,并优化了资源利用。其增强的调试能力提供了前所未有的可视性,支持深度信号追踪、复杂触发条件设置以及与软件仿真的协同调试,使定位和修复缺陷的效率倍增。

3. 全面的生态系统与云端就绪: 该系统深度集成于西门子广受赞誉的Xcelerator数字孪生平台,能够与逻辑仿真、形式验证、虚拟原型等工具无缝衔接,形成完整的数字孪生验证闭环。平台设计充分考虑了云部署的需求,支持弹性扩展,使全球各地的工程团队能够随时随地访问强大的验证资源,实现灵活的、基于需求的验证即服务(VaaS)。

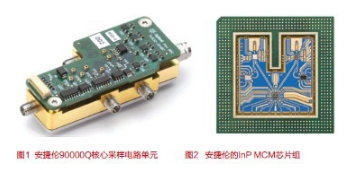

4. 应对特定设计挑战: 针对人工智能加速器、高性能网络芯片等特定领域对高带宽和低延迟的极致需求,新系统提供了优化的接口和内存子系统,能够更真实地模拟最终产品的运行环境。

西门子数字化工业软件高级副总裁表示:“下一代全面硬件辅助验证系统是我们对客户承诺的兑现——帮助他们以更快的速度、更高的信心将创新产品推向市场。它将硬件辅助验证从一项‘加速工具’提升为整个芯片设计与验证生命周期中的战略支柱。”

业界专家分析认为,西门子的此次发布,不仅是一次产品的迭代升级,更是对集成电路设计方法学的一次重要推动。它通过硬件辅助验证的全面化、智能化和云化,有效弥合了设计与验证、硬件与软件、本地与云端之间的鸿沟。对于正处于激烈竞争中的全球芯片设计公司而言,采用此类先进平台,意味着能够更早启动软件开发、更早进行系统集成测试、更早发现潜在风险,从而在决定性的“上市时间”竞赛中占据先机,最终在数字经济时代赢得核心竞争力。